4.7 Cache的基本原理

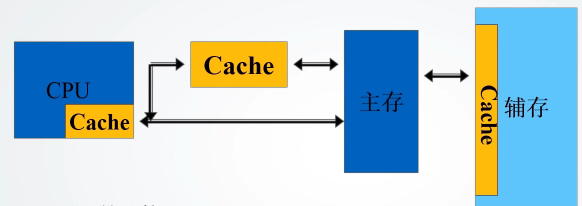

在存储系统的层次结构 提到过,Cache是基于程序局部性原理来缓解CPU与慢速主存之间的速度差异;

但其实整个计算机系统中任何存在速度差异的地方都存在高速缓冲存储器,本节讲到高速缓冲存储器主要是CPU和主存之间的高速存储器;

一、Cache的工作过程

(1)Cache的读操作:

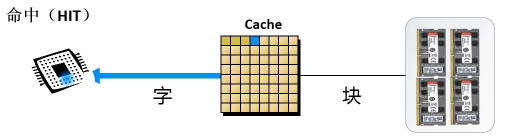

CPU对高速缓冲存储的访问是因为在指令执行过程中,提出了访问主存的要求;

CPU和cache之间每次交换一个字,而主存和cache之间每次交换一个数据块;

如果CPU根据访问的地址在cache中找到了所需要的内容, 则称为cache命中(HIT);

在读取cache中信息的过程中可能会出现如下问题:

1、如何判断数据是否在cache中?

2、当主存中数据被修改后(DMA修改主存),cache中的数据是否有效?

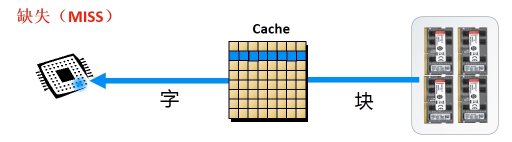

但并不是CPU每一次访问cache都能找到信息,找不到的情况称为cache缺失(MISS)。一旦找不到信息,CPU只能在主存中去寻找,找到之后主存会直接将CPU需要的字传送给CPU,同时将该字所在数据块存到cache中;

(2)Cache的写操作:

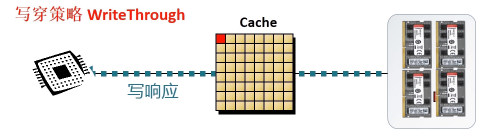

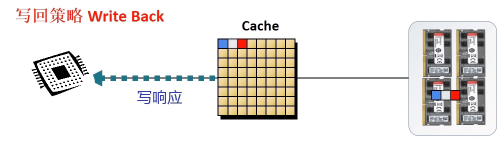

Cache的写操作共有两种策略:1. 写穿策略(Write Through)2.写回策略(Write Bcak)

1、写穿策略(Write Through)

CPU在根据主存地址写cache的同时,也要把信息写回主存中的去;

只有将数据写回主存之后,才能得到写完成的响应;

2、写回策略(Write Bcak)

CPU只将数据写入cache,随后cache返回写完成响应;

然后cache将CPU写入的数据回存到主存中去;

写回策略也会遇到读操作cache命中时的问题:

在cache向主存中回存前, 如果外围设备有DMA操作读数据的请求,此时读到的将不是最新的数据;

二、Cache地址映射机制

因为Cache的目的是缓解CPU与慢速主存之间的速度差异,因此cache在访问机制上有更加快速的机制,主要通过地址映射机制来实现快速访问;

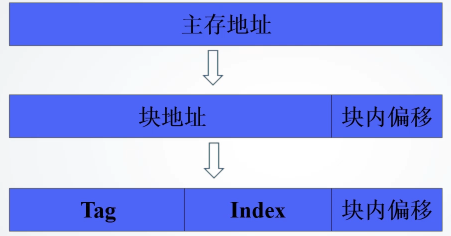

由于主存和cache之间以数据块传输信息,所以有了cache之后要对主存的一维地址做二维划分。即每一个地址要知道在哪一块(块地址),且还要知道在块中的哪一个位置(块内偏移);

仅仅是这样还不够,还要将块地址分为标记部分(Tag)和索引部分(Index);

标记部分用来判断数据是否在cache中,索引部分用来表示在cache的哪一个位置读写数据;

数据分块缩小了数据的寻找范围,索引和标记又为寻找数据指明了方向,为cache提供了快速的访问机制;

三、Cache的结构

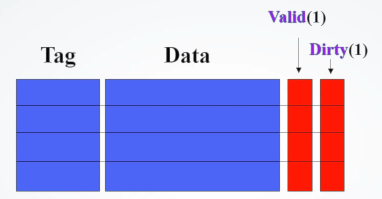

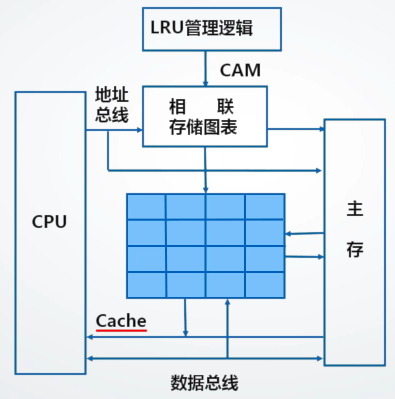

Cache内部结构如图示:

Cache被分成若干行,每行的大小与主存块相同;

Cache每行包含四部分:Tag、Data、Valid、Dirty;

Tag用来判断数据是否在Cache中

Data是与主存交换的数据块

Valid表示Cache中的数据是否有效(参考之前读操作产生的问题)

Dirty表示主存中的数据是否为最新

Cache原理图:

CPU根据得到一个主存地址,先在相连存储表中判断要找到地址的数据是否在cache中(相连存储表是从主存中剥离出的Tag部分);

如果要找的数据在Cache中,则有Cache直接向CPU提供数据;如果不在,则CPU访问主存,找到数据之后,数据直接通过数据总线传给CPU,将数据所在的数据块搬到cache特定行的数据存储体部分(Data部分);

每一次cache中缺数据的时候,主存都会向cache中搬入新的数据块,因此还涉及一个数据块的替换策略(以后再讲)。