4.6 多体交叉存储器

多体交叉存储器的提出目的是为了缓解快速的CPU与慢速的主存之间的速度差异;

与高速缓冲存储器不同,多体交叉存储器不提高存储器速率、不扩展数据总线位数。

而是通过存储芯片的交叉组织, 提高CPU单位时间内访问的数据量,来达成目的;

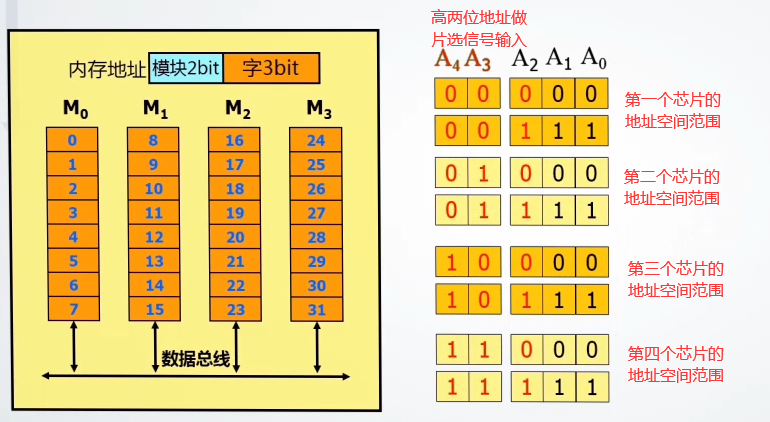

一、 高位多体交叉存储器的组织方式

假设有四片存储芯片,每一个存储芯片的容量是8个存储单元,因此每一个存储芯片有三位地址线,CPU多余地址的高两位地址的作为片选信号输入;

(其实就是存储芯片的字扩展 )

图中可以清晰地看到四片存储芯片当中数据地址的特征,相邻地址的数据存储在一个存储体中,并且多个存储器芯片串行工作。

在这种地址组织形式下,只需要一个地址寄存器即可,不必为每一个芯片都配一个地址寄存器。(因为在这种组织形式下,由于程序局部性原理,要寻找的地址很有可能都在一个芯片当中,只有当一个数据访问完之后,才能访问下一个数据)

这种串行工作无法提高CPU访问存储器的性能;

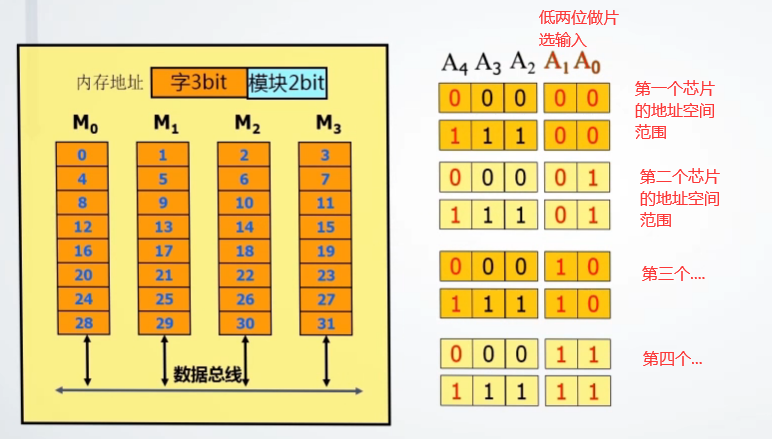

二、低位多体交叉存储器的组织方式

低位多体交叉与高位多体交叉的不同点在于,当在做字扩展时,将CPU多余地址的低两位地址作为片选信号输入,而存储单体的地址则与CPU高三位地址相连;

这种片选信号的产生方式,会带来存储单体内,数据地址特征的明显变化;

第一个芯片在高位多体交叉存储的组织形式中,地址范围是0,1,2,…,8;

而在低位多体交叉存储的组织形式中,第一个芯片的地址范围是0,4,8,…,28;

在低位多体交叉存储的组织形式中,四个存储芯片是并行工作的,且相邻地址处在不同的存储体中,因此就可以实现存储体的并行访问;

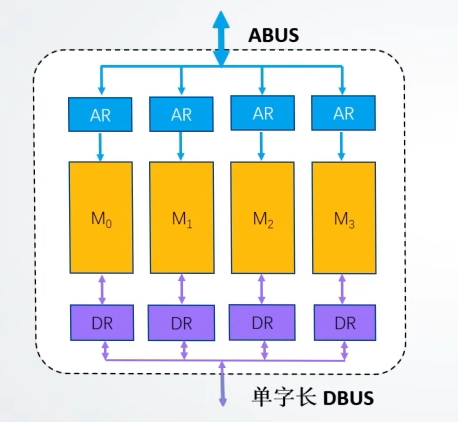

为了并行访问,每一个存储体均需要一个地址寄存器;

这种并行的特征加快了CPU访问存储体的性能,因为CPU不必等待每一个数据在存储体中的访问过程,因此可以连续的对多个存储体进行访问;

通过4个存储体的并行工作,可实现对存储器的流水线方式访问;

假如CPU要在四个存储体中访问四个连续存储的数据,每一个数据的地址会依次通过地址总线输送到地址寄存器中。

当一个地址寄存器接收到地址之后不能马上接受下一个地址,还需要对存储器进行访问和一些其他复杂的过程(涉及寄存器的实现原理),此时在并行模式中不必去等待该寄存器,而是可以直接将下一个数据的地址传送到下一个地址寄存器中去;

(具体流程等会能够看到)

如果存储体系设计的好的话,当最后一个地址寄存器接收到地址之后,第一个存储器的数据访问已经完成了,随即又可以接受地址了;

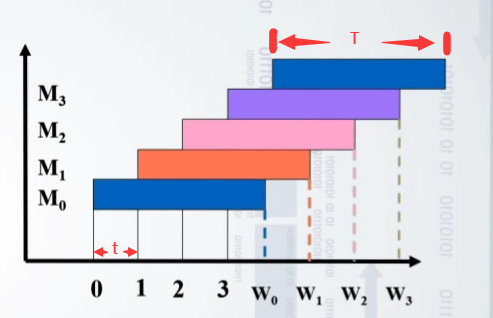

三、低位多体交叉存储器的性能分析

设存储周期为T,总线传送周期为t,交叉模块数为m。

T为寄存器收到地址之后对存储体操作的周期

t为地址总线传送一个地址的周期

m为交叉存储器的数量

则流水线方式存取的条件应满足:T=m∗t

在上一个图对应的四个存储芯片字扩展低位多体交叉存储器中,假设从M0开始,有五个连续数据要被访问,那么对四个芯片的访问和时间满足如下关系:

图中,M0存储芯片接受到总线的地址后需要花费T的时间完成对存储器的读写操作。

每隔t的时间,下一个数据的地址就会通过总线传送给下一个存储芯片;

当经过了一个轮回之后,恰好M0存储芯片操作周期结束,又可以接收一个新的地址;

在高位多体交叉存储器中顺序读m个字的时间为:t1=T∗m;

而在低位多体交叉存储器中并行读m个字的时间为: t1=T+(m−1)∗t;

通过比较,并行方式显然比串行方式快的多;

很通透,看懂了!特地登录感谢一些你

对人有帮助就很开心(º﹃º )

Peter学长加油!!!!

### 学弟也要加油!