只读存储器ROM

不论ROM如何发展,其基本框架都没变,都是前级地址译码器驱动行*列的存储阵列。

发生改进的是存储整列中存储单元内部的结构和工艺。

一、掩膜ROM:

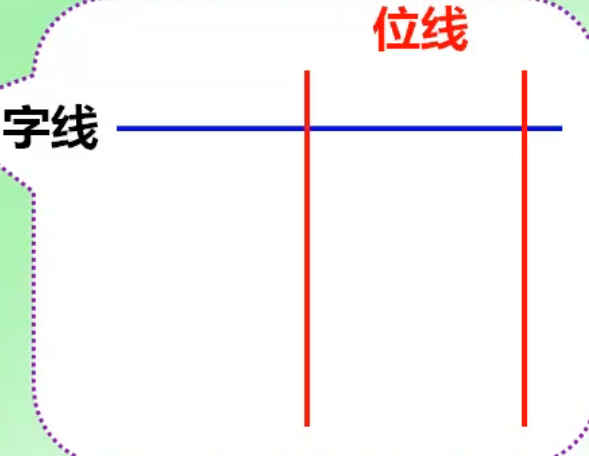

例如在存储阵列的同一行中有两个相邻的存储单元:

与这两个单元相关的包括该行连出的一根字线和两根位线,字线与位线像交叉,但并未连接:

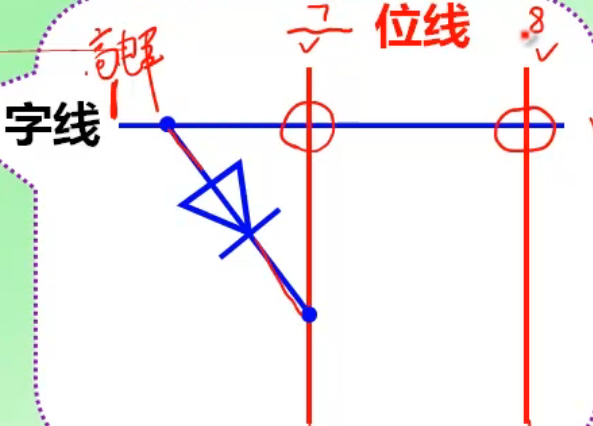

假如地址译码器选中了这个字(行),则该字线会产生一个高电平;

由于字线和位线并未连接,所以字线的高电平并不会对位线产生影响。

但是如果在字线和位线之间连接一个二极管,则字线的高电平会对位线产出影响,位线同样会变为高电平输出1。

也就是说,如果希望掩膜ROM的一个字选通时对应位输出$1$,则字线和对应位之间接一个二极管;

如果希望输出$0$,则不需要更改;

掩膜$ROM$是专门定制的,其内部数值生产出来就已经确定了,是第一代完全符合只读不写的最基本的ROM存储器;

二、PROM:

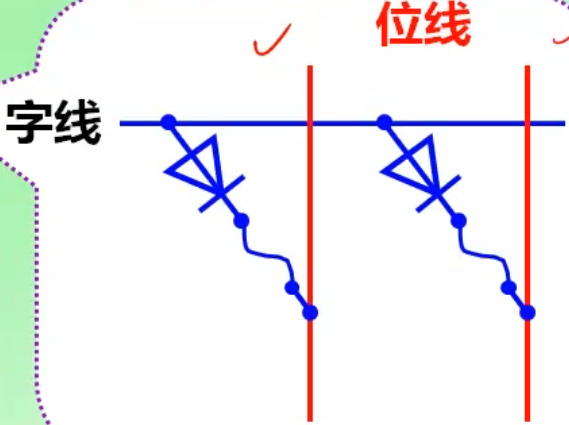

对于$PROM$,出厂时每一个存储单元都是一模一样的连接。

以熔断丝方案为例,每一个存储单元都包含一个熔断丝和一个二极管。

这意味着$PROM$在出厂的时候, 当一个字被选中,字内部初始存储的都是1。

用户拿到之后,可以进行二次编程,可以将指定存储单元的熔断丝烧断,使得该字的对应位存储的值变为$0$。

PROM只能修改一次;

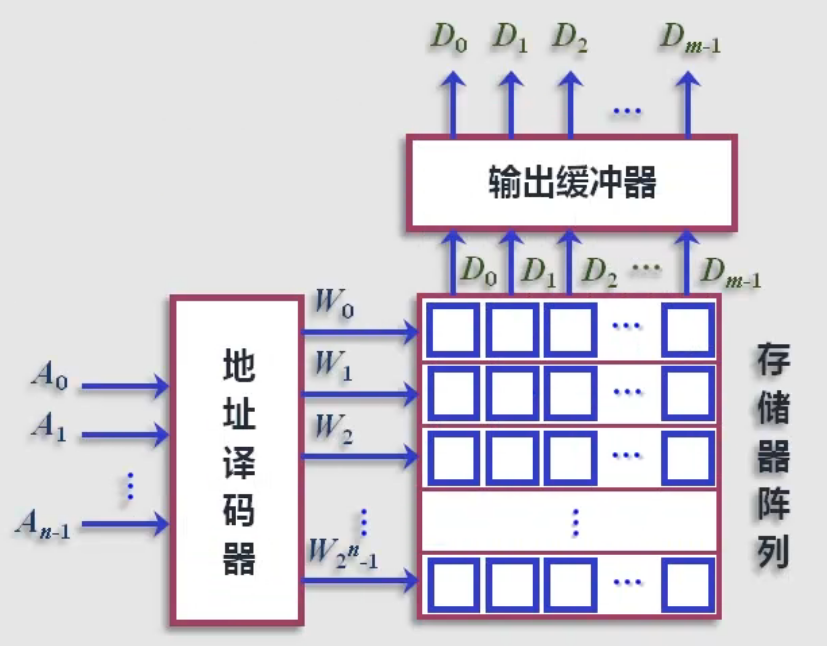

三、ROM的基本结构

对于一个完整地$ROM$,其还包含一个输出缓冲器,三个部分构成$ROM$存储器;

$n$位地址码可以指定$2^n$个字。

$m$个位线,表示每个字所包括的二进制数据的位数(字长),与地址线数量$n$的大小无关。

四、ROM的工作原理

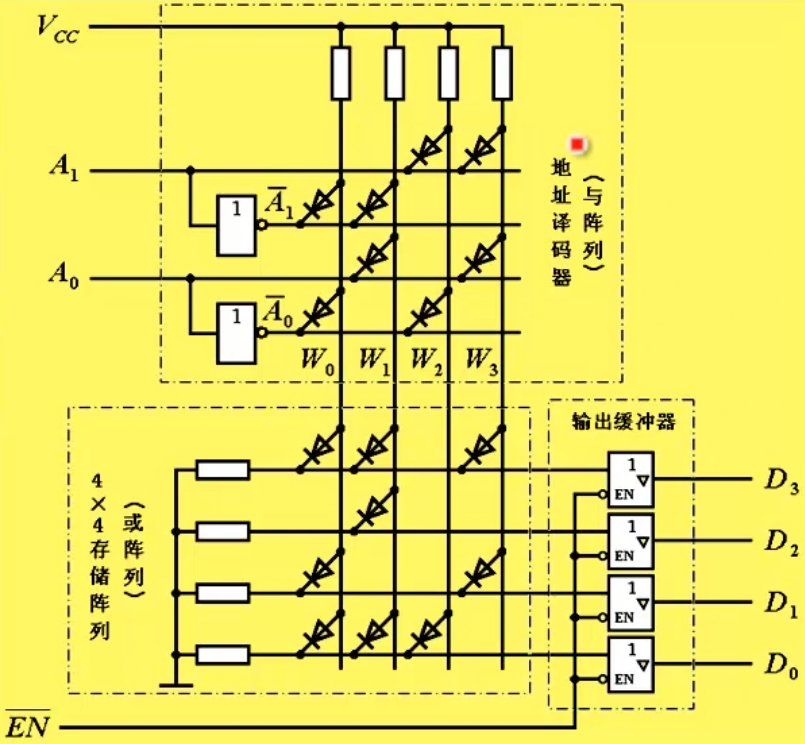

ROM原理框图和结构框图相对应,展现了电路的具体细节;

以一个$2 * 2b$的部分存储器为例:

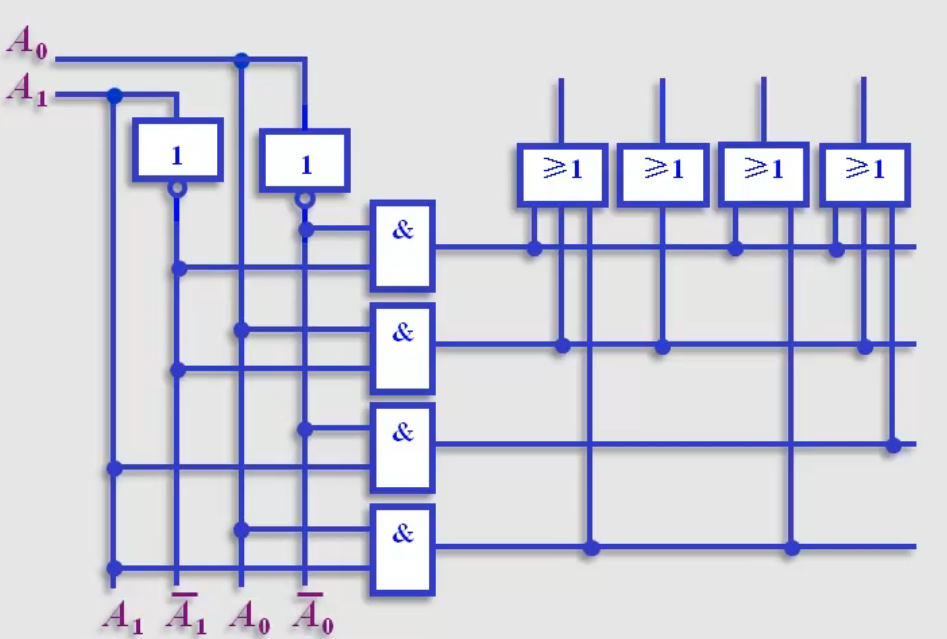

两位输入通过两个非门,获得$A0、\overline{A0}、A1、\overline{A1}$,再通过四个与门唯一确定选中的字(行)。

可见坐半部分的地址译码器其实就是一个与阵列,与结构框图对应;

而存储单元部分的阵列电路其实就是一个或阵列。

当选中一个字时,该字线输出是$1$,其他字线输出是$0$。通过位线和字线的连接,将输入通过一个亦或门得到字中记录的值;

该$ROM$内部存储的数据表如图示:

总结:

-

地址位数决定字的数量

-

输入地址就是字的地址

-

位线的数量就是字的字长

-

字线、位线的数量之间没有必然的决定关系

-

地址译码器是与阵列,存储阵列是或阵列

一个真实的掩膜$ROM$电路如图,与原理中的电路相对应:

$\overline{EN}$是一个控制信号(控制总线),控制对存储单元的读和写;

兄弟大三吗,也要学数电吗

我大二就学过数电了, 复习一下哈哈

冲啊!Peter学长

(^▽^)